|

|

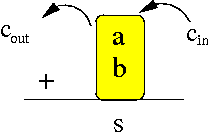

The full adder performs the addition of 2 corresponding bits (a and b) with a carry indication cin:

The sum output

s =

the sum result of the

addition of

a, b and

cin

The cout output

= 1 if the

addition produced a

carry (and

= 0 otherwise)

The logic table of the full adder circuit is as follows:

(inputs) (outputs)

cin a b | cout s

-------------+----------

0 0 0 | 0 0

0 0 1 | 0 1

0 1 0 | 0 1

0 1 1 | 1 0

1 0 0 | 0 1

1 0 1 | 1 0

1 1 0 | 1 0

1 1 1 | 1 1

|

|

We could use the digital circuit design method to construct a (non-optimal) full adder circuit..

Because the full adder is a very important circuit, we have found the optimal solution:

DEMO: /home/cs355001/demo/circuits/1-full-adder.m

|

I will now show the design of a ripple carry adder to add binary numbers of (upto) 4 bits

The design can be easily generalized for binary numbers of any number of bits

The 4 bits ripple carry adder adds two 4-bits (binary) numbers ( a3a2a1a0 +b b3b2b1b0 ):

The

sum of the

addition is

s3s2s1s0

And

cout = 1

if the

addition

produced a carry

output

(and cout = 0

otherwise)

We start with putting down the inputs and outputs of the circuit:

Add the last pair of binary digits using one full adder circuit:

The Carry Input = 0 because there were no previous additions !

Then: add the next pair of binary digits using the carry from the previous full adder:

Next: add the next pair of binary digits using the carry from the previous full adder:

Finally: add the last pair of binary digits using the carry from the previous full adder:

DEMO: /home/cs355001/demo/circuits/4-bit-adder.m

|

|

|

Previously, you saw the 4-bit-adder circuit in EDiSim code using non-array signal notation:

Define FourBit_Adder a3 a2 a1 a0 b3 b2 b1 b0 | CarryOut s3 s2 s1 s0; Full_Adder ch ZERO a0 b0 | c1 s0; Full_Adder cf c1 a1 b1 | c2 s1; Full_Adder cd c2 a2 b2 | c3 s2; Full_Adder cb c3 a3 b3 | CarryOut s3; Endef; |

It is rather cumbersome to write a long series of digits

Using the array signal notation of EDiSim, the same circuit can be re-written more succinctly as:

Define FourBit_Adder a[3..0] b[3..0] | CarryOut s[3..0]; Full_Adder ch ZERO a[0] b[0] | c1 s[0]; Full_Adder cf c1 a[1] b[1] | c2 s[1]; Full_Adder cd c2 a[2] b[2] | c3 s[2]; Full_Adder cb c3 a[3] b[3] | CarryOut s[3]; Endef; |

Note that we must change a0 ⇒ a[0], a1 ⇒ a[1], ... b0 ⇒ b[0], b1 ⇒ b[1],... s0 ⇒ s[0], s1 ⇒ s[1],... inside the body of the definition !!!

(Because: a0 ≠ a[0], a1 ≠ a[1], ... b0 ≠ b[0], b1 ≠ b[1],... s0 ≠ s[0], s1 ≠ s[1],... !!!)

DEMO: /home/cs355001/demo/circuits/4-bit-adder.arr